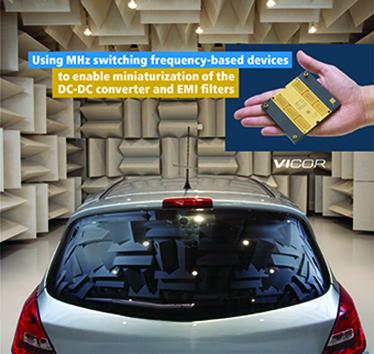

MHz switching frequency-based devices enable miniaturization of the DC-DC converter and EMI filters

Achieving EMI conducted emission compliance for automobiles with a single stage filter. By Nicola Rosano, Sr. Strategic FA/System Engineer at Vicor

More details...

A full brick package developed by TDK-Lambda, the PF1500B-360, is for high voltage distributed power architectures

More details...

The System Management Interface Forum (SMIF Inc.) has announced the latest version of its System Management Bus (SMBus) specification. Version 3.0 is backwards compatible and incorporates a number of major revisions to ease implementation for users of the protocol, significantly broaden performance capabilities to ensure compatibility with the latest topologies and harmonize the specification with the I²C and Power Management Bus (PMBus™) specifications.

The SMBus is a two-wire interface through which system component chips and devices can communicate with each other and with the rest of the system. SMBus is designed to provide a control bus for system and power management related tasks and may be used instead of individual control lines to pass messages to and from devices. In addition to reducing pin counts and supporting a flexible and expandable environment, SMBus delivers a useful range of functionality such as saving states from a suspended event and the reporting of errors.

The SMBus is a two-wire interface through which system component chips and devices can communicate with each other and with the rest of the system. SMBus is designed to provide a control bus for system and power management related tasks and may be used instead of individual control lines to pass messages to and from devices. In addition to reducing pin counts and supporting a flexible and expandable environment, SMBus delivers a useful range of functionality such as saving states from a suspended event and the reporting of errors.

Recognizing the ability of the latest processors and custom logic to work at greater speeds, the 100 kHz bus frequency offered by SMBus 2.0 is complemented with two further speeds of 400 kHz and 1 MHz in the newly announced version 3.0. The addition of these increased speeds has in turn necessitated the adjustment and re-organization of high power electrical drive levels. A further update has seen the data hold time specification changed to match the I²C specification. The decision to align this parameter recognizes that most devices on the market manage data hold time in accordance with I²C.

Version 3.0 also includes the removal of a specification for minimum immunity to noise on the clock and data lines as the SMIF Working Group found that no supplier of SMBus devices or system OEM using SMBus ever tested against the parameter. Other changes include the re-use of defunct special bus addresses (formerly reserved for ACCESS Bus host and ACCESS Bus default address) for the zone read and write protocols that were introduced in revision 1.3 of the PMBus specification, an increase from 32 to 255 for the maximum number of bytes allowed in the write-block read process call, and the addition of protocols to read 32 and 64 bits of data in a single transaction.

Importantly, the changes to the SMBus specification will also support further improvements in the PMBus protocol standard. These improvements will be incorporated in the upcoming PMBus 1.3.1 specification.

| Privacy Policy | Site Map | © Copyright DFA Media

| Web design by Immersive Media